# EGC442 Class Notes 4/21/2023

**Baback Izadi** Division of Engineering Programs bai@engr.newpaltz.edu

|         |  | Test 1 | Test 2 |

|---------|--|--------|--------|

| Average |  | 82.5   | 88.5   |

| Median  |  | 85.5   | 89.0   |

| MAX     |  | 92.0   | 95.0   |

| Minimum |  | 67.0   | 80.0   |

Bob is building a fence behind his house. He uses a hammer to attach a board to the rail. Bob then measures and cuts the next board.

The likelihood that Bob will need the hammer again is an example of \_\_\_\_\_ locality.

- O spatial

- temporal

- Bob is building a fence behind his house. He grabs a hammer from the garage. Bob will likely need additional tools stored in the garage, so Bob also grabs nails, a shovel, and a level.

The likelihood that Bob will need resources stored together in the garage is an example of \_\_\_\_\_ locality.

#### spatial

O temporal

Given the following loop, the high likelihood of accessing multiple elements within array A is an example of \_\_\_\_\_ locality.

while (i < 10){

A[i] = A[i] + 2;

i = i + 1;</pre>

spatial

3

O temporal

Given the following loop, the high likelihood of accessing i = i + 1 repeatedly is an example of \_\_\_\_ locality.

#### while (i < 10){ A[i] = A[i] + 2;

i = i + 1;

O spatial

temporal

5) Instructions may exhibit temporal locality, but never spatial locality.

6) Data may exhibit spatial locality, but never temporal locality.

⊖ True

🖲 False

O True

False

#### Correct Bob will

Bob will likely need to use a hammer several times during the construction of the fence. The reuse of a specific resource within a short time is known as temporal locality.

#### Correct

Bob will need a variety of tools during the construction of the fence. These tools are likely stored in a similar location, such as the garage. The use of resources stored closely together is known as spatial locality.

#### Correct

Programs commonly step through an array, and access each element sequentially.

#### Correct

Most programs contain loops, so the same subset of instructions are executed repeatedly.

#### Correct

Instructions may exhibit both temporal and spatial locality. Instructions are accessed sequentially in the absence of a jump, thus showing spatial locality. Instructions within a loop are executed repeatedly, thus showing temporal locality.

#### Correct

Data may exhibit both spatial and temporal locality. Sequential access to arrays or strings show spatial locality. Data within a loop are accessed repeatedly, thus observe the neural locality. A memory hierarchy is composed of an upper level and a lower level. Data is requested by the processor. 9 out of 10 requests find the data in the upper level and returns the data in 0.4 ns. The remaining requests require 0.7 ns to return the data.

Determine the corresponding values for the upper level memory.

| 0.9 | $\frac{\text{Mit rate}}{\text{total number of memory accesses}} = \frac{9}{10} = 0.9$                                                                                       | Correct |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0.1 | Miss rate<br>(1 - hit rate) = (1 - 0.9) = 0.1                                                                                                                               | Correct |

| 0.4 | Hit time<br>Data in the upper level requires 0.4 ns to retrieve.                                                                                                            | Correct |

| 0.7 | Miss penalty<br>0.7 ns is required to replace a block in the upper level with the corresponding block from<br>the lower level, and then deliver the block to the processor. | Correct |

| Seek time          | The time required to move the head to the desired track.<br>The first step to access data from a magnetic disk is to position the head over the<br>proper track. Average seek times are usually advertised as 3 ms to 13 ms, but the actual<br>seek time may be much faster due to the locality of disk references. |         |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Rotational latency | The time required for the desired sector to rotate under the head.<br>The second step to access data from a magnetic disk is to rotate the platter so that the desired sector is positioned under the head. The average latency is halfway around the disk, or 2 to 5.6 ms.                                         | Correct |  |

| Transfer time      | The time required to transfer a block of bits.<br>The third step to access data from a magnetic disk is to transfer the data from the disk to the processor. Transfer rates in 2012 were between 100 and 200 MB/sec, but built-in caches can improve transfer rates to 750 MB/sec.                                  | Correct |  |

Select the memory technology that most closely matches the statements below.

- 1) Used to implement the memory levels closest to the processor.

- SRAM

- O DRAM

- 2) Has fewer transistors per bit of memory.

- O SRAM

- DRAM

# 3) Requires a periodic refresh.

- O SRAM

- DRAM

# Correct

SRAMs are typically faster, so are used to implement memory levels closer to the processor. SRAM access times typically range from 0.5 to 2.5 ns, while DRAM access times typically range from 50 to 70 ns.

# Correct

DRAMs use a single transistor (and capacitor) per bit of memory. In contrast, SRAMs typically use six to eight transistors per bit of memory.

# Correct

DRAMs store a value as a charge in a capacitor, which can only be kept for several milliseconds. Thus, values are periodically refreshed by reading and writing the value back to the cell.

# 1) A magnetic disk is a type of \_\_\_\_\_.

- e mechanical device

- O semiconductor memory

2) Writes to the same location in a \_\_\_\_\_ can wear out memory bits.

- flash memory

- O magnetic disk

# Memories in personal mobile devices are typically \_\_\_\_\_.

- flash memory

- O magnetic disk

In a magnetic disk, sequential block numbers are placed next to one another on a track. Ex: Block 207 is placed after block 206.

○ True

🖲 False

5) Magnetic disks are volatile.

○ True

🖲 False

# Correct

A magnetic disk is composed of a collection of platters, which rotate on a spindle. A movable arm positions a small electromagnetic coil just above each platter, which is responsible for reading and writing to the disk.

# Correct

Flash memory can support a finite number of writes because the underlying technology deteriorates from frequent use. Over time the location is no longer able to store data. Most flash memories use a technique called wear leveling to move blocks from frequently written locations to less used locations.

### Correct

Magnetic disks typically have higher capacity and lower cost, but the mechanical components are not well suited for the jostling inherent in personal mobile devices, and may consume more power too.

## Correct

Sequential blocks may be on different tracks. To speed up sequential transfers, blocks are ordered in serpentine fashion across a single surface, trying to capture all the sectors that are recorded at the same bit density.

## Correct

The metal platters are covered with magnetic recording material used to store data. The recording material is not dependent on a power source and maintains the data even when the power is removed.

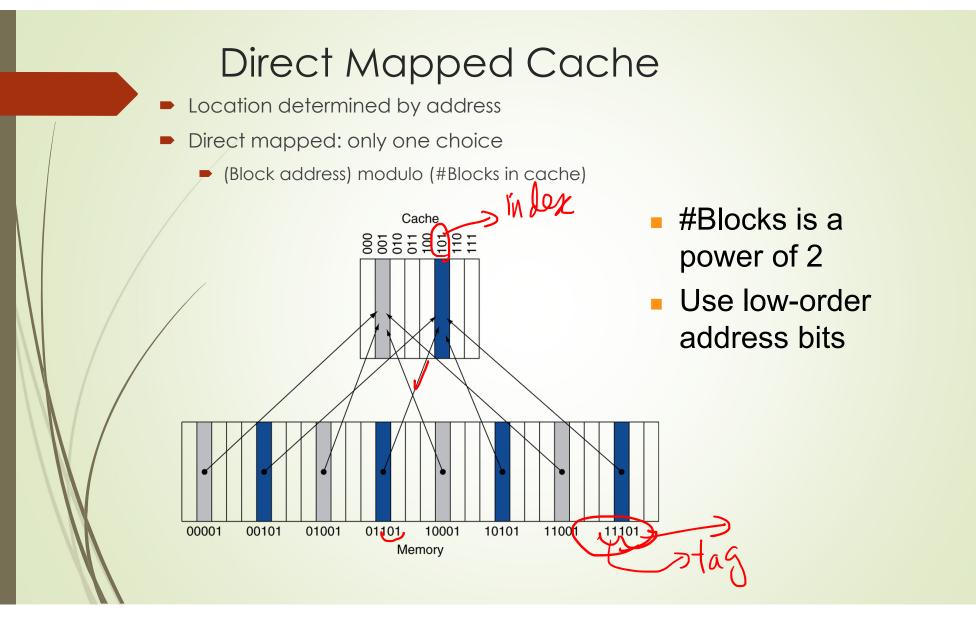

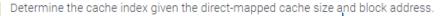

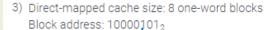

# Direct-mapped cache size: 8 one-word blocks Block address: 101012

101 Check Show answer

# Check Show answer

Check

101

4) Direct-mapped cache size: 16 one-word blocks Block address: 00101100

1100

Show answer

# Correct

011

= (Block address) modulo (Number of blocks in the cache)

=  $00011_2 \mod 1000_2$

# = 011<sub>2</sub> 3<sub>10</sub> in 3-bit binary is 011

# Correct

# 101

The index could be determined using base 10 calculations: (21) modulo (8) = 5. However, the number of cache entries is a power of 2, so the cache index can be determined by the low-order log<sub>2</sub> (cache size in blocks) bits of the block address. Log<sub>2</sub>(8) is 3 so:  $10101_2$  (Note that  $101_2$  is  $5_{10}$ ).

# Correct

# 101

The cache index is the lowest order 3 bits of the block address, which is independent of the size of the block address.

# Correct

# 1100

This cache contains 16 blocks, so the cache index is determined by the lowest order log\_2(16). Log\_2(16) is 4 so: 00101100\_2  $\,$

#### Correct

The lower 3 bits of the address (101) specifies the cache block mapping. The cache block's valid bit is turned off (N), which indicates the cache block does not contain valid data.

The request to address 00110 two results in a cache miss, so the word at address 00110 two is brought into cache

specifies the cache block mapping, and the upper 2 bits

block 110<sub>two</sub>. The lower 3 bits of the address (110)

of the address (00) becomes the tag.

-> nover been

# miss

2) After a request to address  $00110_{two}$  the tag in cache block  $110_{two}$  is

#### 00 💿

A request to address 00001<sub>two</sub> results in a cache \_\_\_\_\_.

|   | Index | v | Таг               | Data                           |

|---|-------|---|-------------------|--------------------------------|

| [ | 000   | Y | 01 <sub>two</sub> | Memory (01000 <sub>two</sub> ) |

| - | 001   | Y | 11 <sub>twp</sub> | Memory (11001 <sub>two</sub> ) |

| 1 | 010   | Y | 01 <sub>two</sub> | Memory (01010 <sub>two</sub> ) |

|   | 011   | Υ | 00 <sub>two</sub> | Memory (00011 two)             |

|   | 100   | Ν |                   |                                |

|   | 101   | Ν |                   |                                |

|   | 110   | Ν |                   |                                |

| ľ | 111   | N |                   |                                |

#### Correct

Correct

The request results in a miss because the tag in cache block 001<sub>two</sub> does not match the upper two bits of address  $00001_{two} (11_{two} \neq 00_{two})$ .

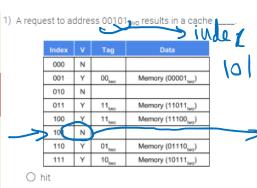

4) After a request to address 00101  $_{\rm two}$  the data in cache block 101  $_{\rm two}$  is Memory(\_\_\_\_\_two).

| Index | v | Tag               | Data                           |

|-------|---|-------------------|--------------------------------|

| 000   | Y | 01 <sub>two</sub> | Memory (01000 <sub>5eo</sub> ) |

| 001   | N |                   |                                |

| 010   | Ν |                   |                                |

| 011   | Y | 00 <sub>two</sub> | Memory (00011 bec)             |

| 100   | N |                   |                                |

| 101   | Y | 11 <sub>two</sub> | Memory (11101 <sub>beo</sub> ) |

| 110   | Y | 00 <sub>two</sub> | Memory (00110 <sub>beo</sub> ) |

| 111   | N |                   |                                |

# 1110100101

00101

5) A request to address 10111<sub>two</sub> results in a cache \_\_\_\_\_

| 000 |   |                    |                                |

|-----|---|--------------------|--------------------------------|

| 001 | N |                    |                                |

| 010 | Y | 11, <sub>two</sub> | Memory (11010 <sub>two</sub> ) |

| 011 | N |                    |                                |

| 100 | Y | 10 <sub>two</sub>  | Memory (10100 <sub>two</sub> ) |

| 101 | N |                    |                                |

| 110 | Y | 00 <sub>two</sub>  | Memory (00110 <sub>two</sub> ) |

| 111 | Y | 10 <sub>two</sub>  | Memory (10111 <sub>two</sub> ) |

# 🖲 hit

() miss

6) After a request to address  $10000_{\rm two}$  the data in cache block  $000_{\rm two}$

| Index | v | Tag                | Data                           |

|-------|---|--------------------|--------------------------------|

| 000   | Y | 10 <sub>two</sub>  | Memory (10000 <sub>beo</sub> ) |

| 001   | Υ | 00 <sub>two</sub>  | Memory (00001 two)             |

| 010   | Υ | 11 <sub>two</sub>  | Memory (11010 <sub>two</sub> ) |

| 011   | Y | 11, <sub>two</sub> | Memory (11011 <sub>beo</sub> ) |

| 100   | Y | 10 <sub>two</sub>  | Memory (10100 <sub>two</sub> ) |

| 101   | Y | 00 <sub>two</sub>  | Memory (00101 <sub>beo</sub> ) |

| 110   | Y | 00 <sub>two</sub>  | Memory (00110 <sub>two</sub> ) |

| 111   | Y | 10 <sub>100</sub>  | Memory (10111 here)            |

#### ○ is empty

does not change

7) Cache block  $111_{two}$  with tag  $00_{two}$  corresponds to memory address

#### Correct

The full address of a word contained in a cache block is the concatenation of the tag field and the index, or 00111  $_{\rm two}{\rm -}$

#### Correct

The request to address 00101<sub>two</sub> results in a cache miss, so the word at address 00101<sub>two</sub> is brought into cache block 101<sub>two</sub> and replaces Memory(11101<sub>two</sub>).

# Correct

The request results in a cache hit. The valid bit is set (Y) so the data is valid. The tag in cache block 111<sub>twe</sub> matches the upper two bits of address  $10111_{twe}$  (10<sub>twe</sub> =  $10_{two}$ ), which indicates that the requested word is in the cache.

#### Correct

The request to address  $10000_{two}$  results in a hit, so the contents of the cache does not change. If a request results in a miss, then the cache is updated with the requested word from memory.

# ⊖ hit

miss

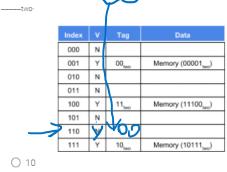

| 11,000 | 16 8  | Yo I          | 2                 |                                | tag | 1 mdex<br>3210 |

|--------|-------|---------------|-------------------|--------------------------------|-----|----------------|

|        | Index | v             | Tag               | Data                           |     |                |

|        | 000   | Υ             | 01 <sub>two</sub> | Memory (01000 <sub>two</sub> ) | ],  |                |

|        | 001   | Ν             |                   |                                |     | 000            |

|        | 010   | $\mathcal{A}$ | Y 40              | Memor H(1010)                  |     |                |

|        | 011   | Y             | 00 <sub>two</sub> | Memory (00011 <sub>two</sub> ) |     |                |

|        | 100   | Ν             |                   |                                |     |                |

|        | 101   | Y             | 11 <sub>two</sub> | Memory (11101 <sub>two</sub> ) |     |                |

|        | 110   | Υ             | 00 <sub>two</sub> | Memory (00110 <sub>two</sub> ) |     |                |

|        | 111   | Ν             |                   |                                |     |                |

MENEINZ -> Miss MENEN2 =

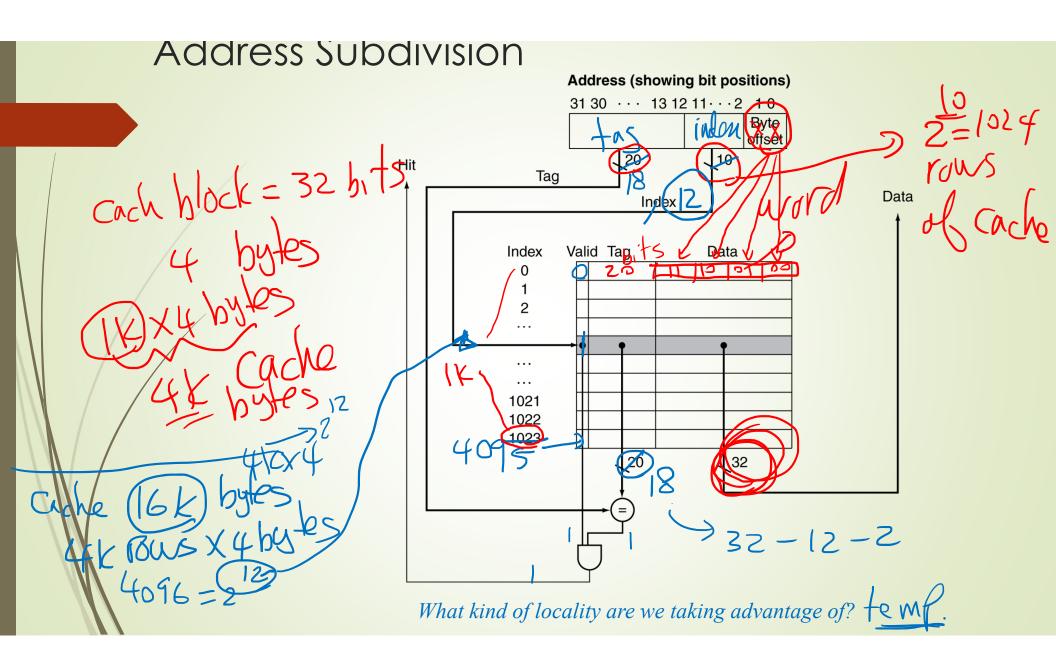

27) Design a direct-mapped cache with the following 2+9=11 parameters: Address (showing bit positions) 31 30 · · · 13 12 11 · · · 2 Address size: 32 bits • Bvte Cache data size: 2 KB Cache block: 1 word, Hit Tag Data index 4 byles 2kB-4=512-5k=512Index Valid Tag Data B2 0 RC 1 2 . . . ... • • • 1021 1022 1023 32 20 Ζ

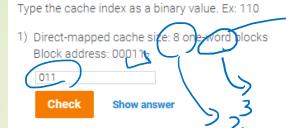

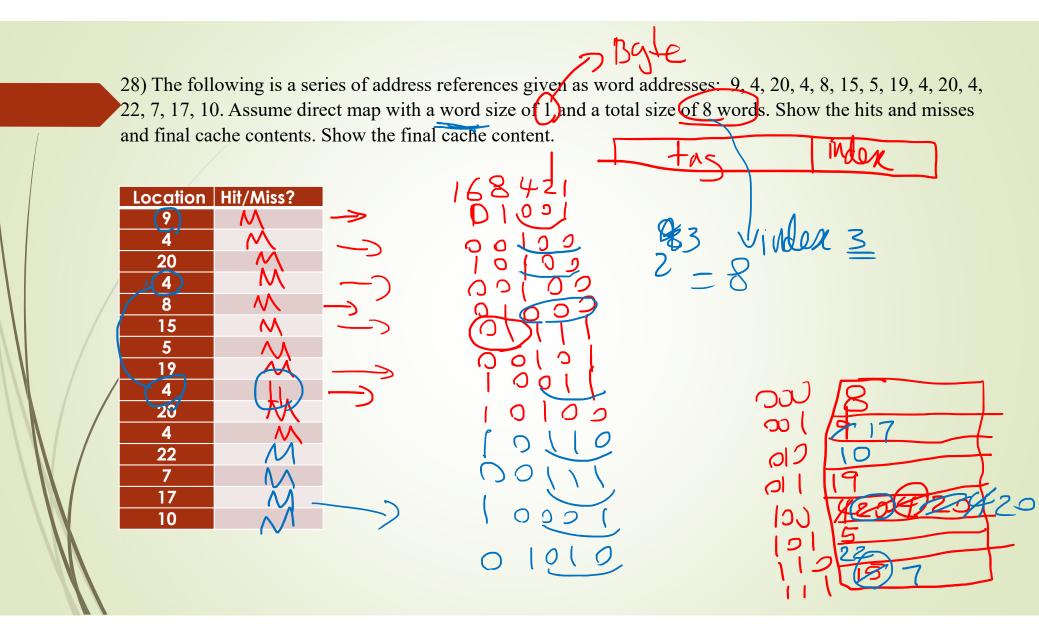

28) The following is a series of address references given as word addresses: (2), 4, 20, 4, 8, 15, 5, 19, 4, 20, 4, 22, 7, 17, 10. Assume direct map with a word size of 4 bytes and a total size of 8 words. Show the hits and misses and final cache contents. Show the final cache content. 3

|   | Location | Hit/Miss?       |      |

|---|----------|-----------------|------|

|   |          |                 |      |

|   | 4        | $\mathcal{M}$   |      |

|   | 20       | M               |      |

| 1 | 4        | <b> </b>        |      |

|   | 8        | $\dot{\lambda}$ |      |

|   | 12       | $\wedge$        | 0100 |

|   |          | •               | CIUO |

| , |          |                 |      |

| / | 4        |                 |      |

|   | 20       |                 |      |

|   | 4        | TI I            |      |

|   | <u></u>  | 11              |      |

|   |          |                 |      |

|   | 47       |                 |      |

|   | 20       |                 |      |

|   | -        |                 |      |